2018年4月,在美国加州第二十四届年度技术研讨会上,台积电首度对外界公布了创新的系统整合单芯片(SoIC)多芯片3D堆叠技术。若以台积电2009年正式进军封装领域估算,SoIC是台积电耗费十年才磨出的实现3D IC的高阶封装技术。

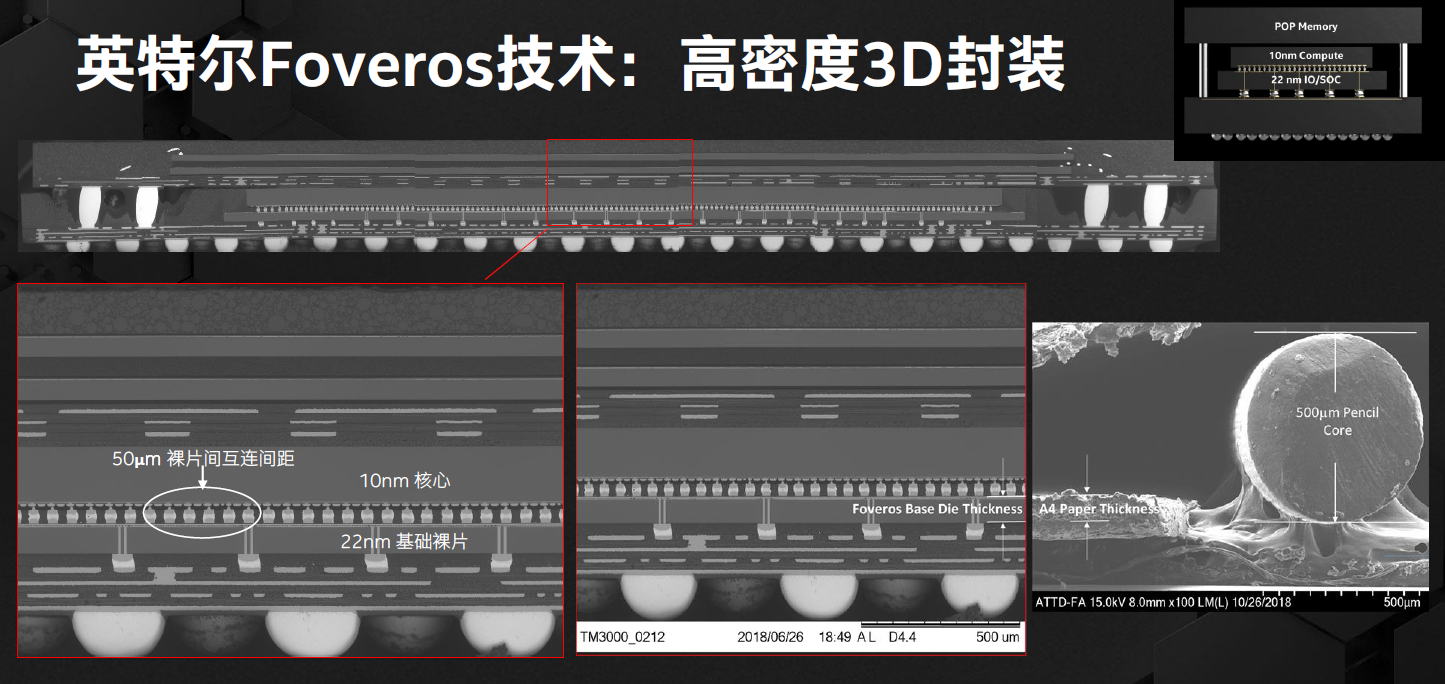

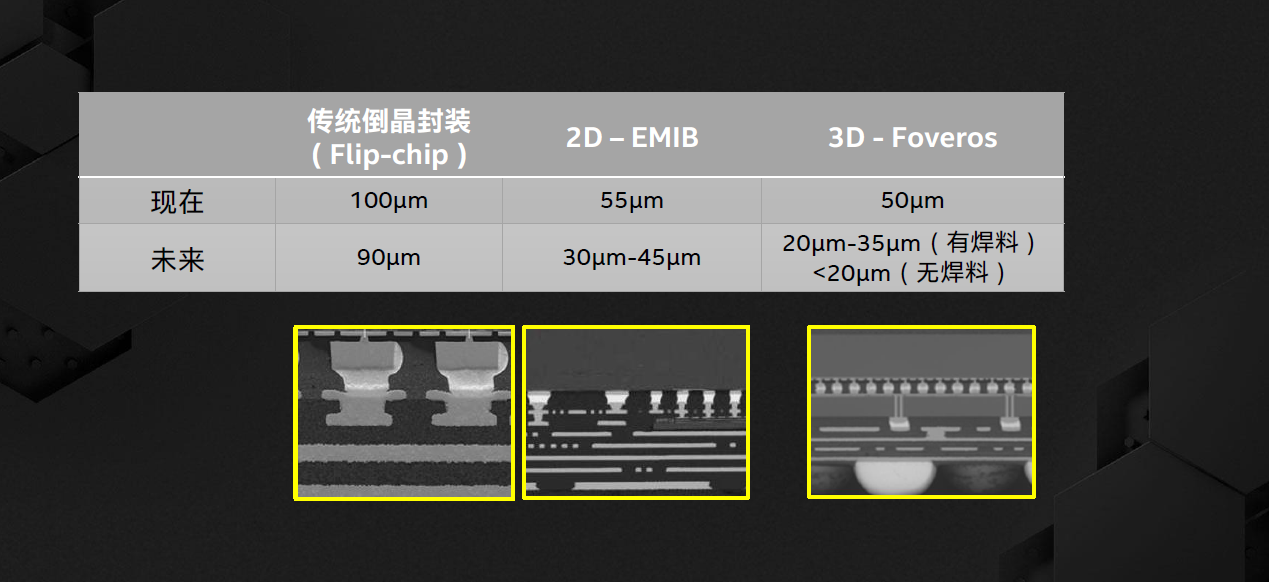

无独有偶,日前,半导体IDM大厂英特尔也在上海召开了先进封装技术解析会,详细介绍了其在今年7月推出的一些列全新封装技术架构的亮点和意义,其中就包括其在2018年12月举行的“架构日”上宣布的3D封装技术Foveros。

该举动显示,在制程和封装领域,英特尔正以跨晶体管、封装和芯片设计的协同优化快速革新。

为什么像英特尔、台积电这样的一直引领半导体产业制程技术发展的厂商都不约而同地把目光聚焦到先进的封装测试技术上呢?

图片来源:英特尔

图片来源:英特尔

放缓的摩尔定律

自第一颗集成电路发明至今,集成电路相关产业已经走过了60年的发展历史。在这60年中,半导体制程技术在摩尔定律的指引下,一路狂奔。

在过去摩尔定律的黄金时期,随着制程的进化,同样的芯片的制造成本会更低,因为单位面积晶体管数量提升导致相同的芯片所需要的面积缩小。所以制程发展速度如果过慢,则意味着芯片制作成本居高不下,导致利润无法扩大。因此,摩尔定律背后的终极推动力其实是经济因素。

不过,最近几年随着制程技术开始跨入10纳米以下的极限领域,受制于工艺、制程和材料的瓶颈,摩尔定律开始呈现疲态。一味的追求先进制程并不能使厂商的经济收益得到最大化。

所以,纯晶圆代工的格芯和联电已经先后宣布终止高端先进制程的研发,止步14纳米,而英特尔在从14纳米向10纳米过渡的过程中也是几经周折。

台面上,目前还在继续研究且有能力部署10纳米以下高端先进的厂商只剩台积电、三星、英特尔三家厂商。

不可否认的是,单纯从制程技术上来看,虽有这几家厂商勉力维持,但摩尔定律确实放缓了。

于是,如何让芯片的性能继续跟随摩尔定律的脚步发展成为了集成电路业者开始探讨的话题,而高端3D封装就是其中一个新的选择。由此,晶圆制造厂商的竞争也从明面上的制程之争转向先进封装的“暗战”,也就有了前述英特尔、台积电等半导体大厂将目光瞄向3D先进封装的事实。

新的突破口

3D封装是在同一个封装体内于垂直方向叠放两个以上芯片的封装技术,它起源于快闪存储器(NOR/NAND)及SDRAM的叠层封装,目前在NAND相关产品领域应用较为成熟。

3D封装改善了芯片的许多性能,如尺寸、重量、速度、产量及耗能。

一般认为,3D封装发展可能会经历以下几个阶段:具有TSV和导电浆料的快闪存储器晶圆叠层得快速发展;随后会有表面凸点间距小至5μm的IC表面-表面键合出现;最后,硅上系统将会发展到存储器、图形和其它IC将与微处理器芯片相键合。

从发展趋势来看,3D封装为各类芯片的异质整合提供了可能,所以被认为是摩尔定律能够延续的新的突破口。

图片来源:英特尔

英特尔在此次解析会上强调其3D封装技术在封装过程中要达到低功耗、高带宽、高性能三大要求。为此,英特尔全面布局了3大全新的封装技术架构:

第一是Co-EMIB技术:基于2D封装的EMIB和3D封装的 Foveros,利用高密度的互连技术,实现高带宽、低功耗,并实现有竞争力的 I/O 密度,全新的 Co-EMIB技术可连结更高的计算性能,能够让两个或多个 Foveros 元件互连,基本达到单晶片性能。

第二是英特尔的互连技术ODI,提供封装中小芯片之间,无论是芯片或模块之间的水平通信或是垂直通信,互联通信都有更多灵活性。

第三是MDIO:是基于先进介面汇流排 AIB( Advanced Interface Bus )发布的 MDIO 全新裸片间接口技术。MDIO 技术支持对小芯片 IP 模块库的模块化系统设计,能够提供更高能效,实现 AIB 技术两倍以上的速度和带宽密度。

这其中核心的部分是英特尔的Foveros技术,该技术通过在水平布置的芯片之上垂直安置更多面积更小、功能更简单的小芯片来让方案整体具备更完整的功能。

例如我们可以在CPU之上堆叠各类小型的IO控制芯片,从而制造出兼备计算与IO功能的产品;或者,我们可以干脆将芯片组(南桥)与各种Type-C、蓝牙、WiFi等控制芯片堆叠在一起,制造出超高整合度的控制芯片。按照英特尔的规划,未来基于Foveros的3D叠加和EMIB的2D叠加这些都在产品路线图上。

有了堆叠方式和架构,英特尔Co-EMIB、ODI、MDIO等互联技术就成为了3D堆叠、甚至3D/2D整合的过程中实现芯片互联且保持灵活性的关键。

英特尔封装技术路线图,图片来源:英特尔

英特尔封装技术路线图,图片来源:英特尔

基于这些先进的封装技术和架构,英特尔表示能够为客户提供各类低功耗、高带宽、高性能的产品。

目前,英特尔第一个采用Foveros封装技术的“ Lakefield ”处理器已经发布。

据介绍,Lakefield是一款针对移动PC的产品,基于英特尔最新的10nm工艺制造,采用Foveros 3D混合封装,集成了一个大核心CPU和四个小核心CPU。

此外,Lakefield还集成了英特尔第11代的核显,以及第11.5代IPU图像处理单元,可以提供从图像输入到显示设备端到端的数据流信号处理的全面支持。支持4×16-bit LPDDR4内存控制器以及多个I/O模块。

Lakefield面向便携式设备,虽有5个核心,但是整个芯片的大小还没有一枚硬币大,并且待机功耗仅有2mW,最大功耗才7W。高达3.1GHz的频率也能够让其处理一些基础的工作。

从参数来看,基于英特尔Foveros 3D封装的Lakefield芯片确实能够大幅提升性能降低功耗,这也算是为延续摩尔定律提供了新的方向。

英特尔的优势

当然,客户或消费者在购买技术或产品的时候不仅仅只是看性能而已。

事实上,半导体科技产业正在经历非常快速的市场转型,过去以硬件和终端为中心的商业模式正在加速向以数据为中心的智能互联世界转变。

随着现代社会的数据量越来越庞大,英特尔也在围绕这几大挑战发力,并且着手开发新的技术以及解决方案,以期能够满足新的商业模式的需求。

全新封装架构和3D封装技术的推出就是英特尔应对制程困境和新的商业环境的具体体现。

从技术层面来看,英特尔Foveros技术对于产业最大的优势在于它可以将过去漫长的重新设计、测试、流片过程省去,直接将不同厂牌、不同IP、不同工艺的各种成熟方案封装在一起,从而大幅降低成本并提升产品上市速度。同时,这种整合程度的提升也能够进一步缩小整体方案的体积,为万事万物的智能化、物联网化打开全新的大门。

与此同时,提供Co-EMIB、ODI、MDIO三大互联技术则是英特尔相比其它3D封装技术来说最大的不同,也是其优势之一。

当然,英特尔最大优势其实来自于其产业链的整合能力,在异构集成时代,IDM的模式让英特尔的优势显化。

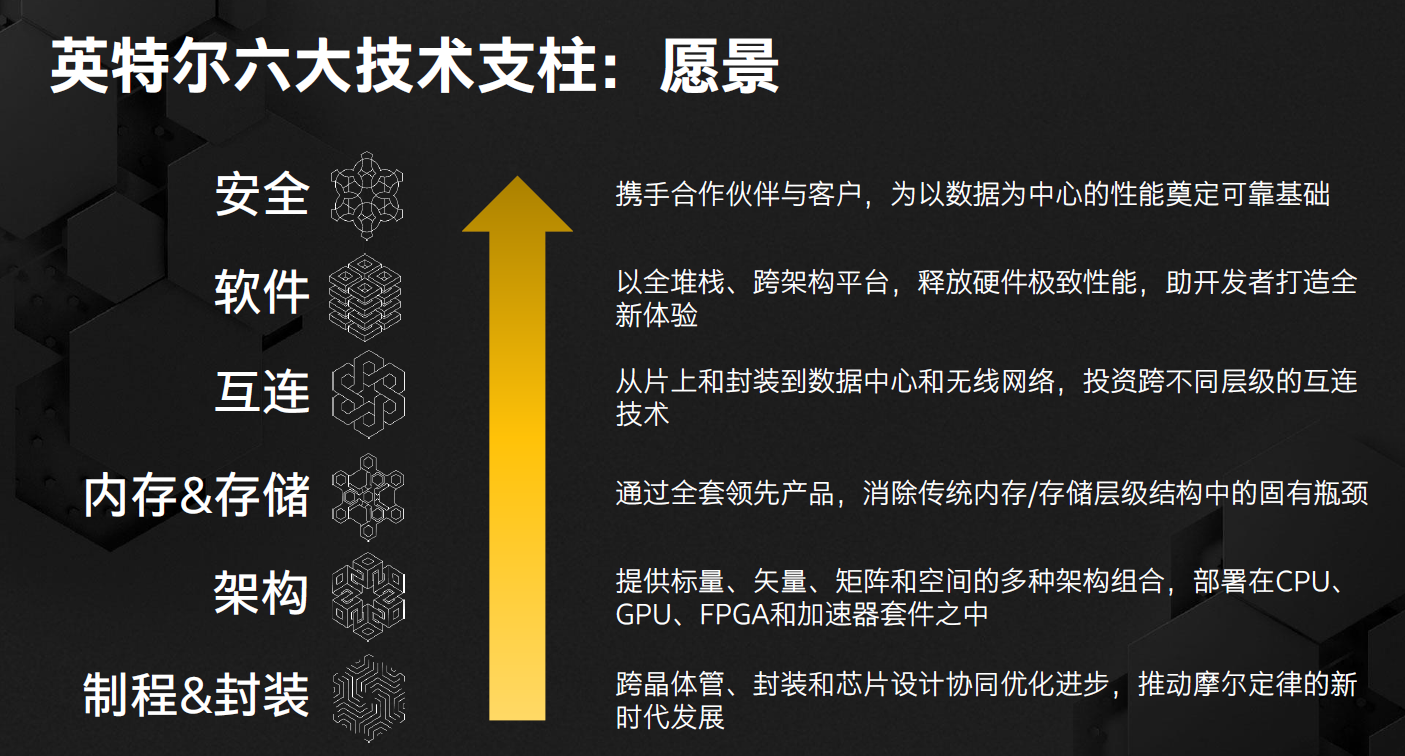

英特尔六大技术支柱,图片来源:英特尔

这两年,?英特尔在多个场合提出了制程和封装、架构、内存和存储、互连、安全、软件为基础的六大技术支柱战略,以应对未来数据量的爆炸式增长、数据的多样化以及处理方式的多样性。

毫无疑问,封装技术被英特尔放在了和制程同等重要的最基础的位置,是其他五大支柱的支撑,也是英特尔参与市场竞争的核心优势。